# F&eIT Series

# Isolated Counter Module CNT24-2(FIT)GY User's Manual

CONTEC CO.,LTD.

# **Check Your Package**

Thank you for purchasing the CONTEC product.

The product consists of the items listed below.

Check, with the following list, that your package is complete. If you discover damaged or missing items, contact your retailer.

Product Configuration List

- Module ...1

- First Step Guide ...1

- CD-ROM [F&eIT Series Setup Disk] \*1 ...1

- Interface connector plugs ...2

- The CD-ROM contains various software and User's Manual (this manual)

Interface connector plugs

First step guide [F&eIT Series Setup Disk]

i

# **Copyright**

Copyright 2001 CONTEC CO., LTD. ALL RIGHTS RESERVED

No part of this document may be copied or reproduced in any form by any means without prior written consent of CONTEC CO., LTD.

CONTEC CO., LTD. makes no commitment to update or keep current the information contained in this document.

The information in this document is subject to change without notice.

All relevant issues have been considered in the preparation of this document. Should you notice an omission or any questionable item in this document, please feel free to notify CONTEC CO., LTD.

Regardless of the foregoing statement, CONTEC assumes no responsibility for any errors that may appear in this document or for results obtained by the user as a result of using this product.

# **Trademarks**

F&eIT is a registered trademark or trademark of CONTEC CO., LTD. Other company and product names that are referred to in this manual are generally trademarks or registered trade trademark.

# **Table of Contents**

|    | Check Your Package                                                                                                                                            | i                          |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1. | Introduction                                                                                                                                                  | 1                          |

|    | Features Functions and control method by controller connected Limited One-Year Warranty How to Obtain Service Liability Handling Precautions About the Manual | 2<br>4<br>4<br>5           |

| 2. | Module Nomenclature and Settings                                                                                                                              | 7                          |

|    | Nomenclature of Module Components  Setting a Device ID  Setup Method  LED Indicator                                                                           | 8                          |

| 3. | Connecting to an External Device                                                                                                                              | 9                          |

|    | Interface Connector                                                                                                                                           | 9<br>0<br>1<br>1<br>2<br>3 |

| 4. | Using the I/O Address Map15                                                                                                                                   | 5                          |

|    | Starting I/O Address                                                                                                                                          | 6<br>8<br>0                |

|    | Operation Commands                               | 22  |

|----|--------------------------------------------------|-----|

|    | Description of Input Commands                    | 23  |

|    | Reading a Count (command CH0: 00h, CH1: 05h)     | 23  |

|    | Status Data (command CH0: 01h, CH1: 06h)         | 24  |

|    | Interrupt Mask (command 15h)                     | 25  |

|    | Sense Port (command 16h)                         | 25  |

|    | Description of Output Commands                   | 26  |

|    | Initial Count Value (command CH0: 00h, CH1: 05h) | 26  |

|    | Operating Mode (command CH0: 01h, CH1: 06h)      | 26  |

|    | Counter Operating Modes                          |     |

|    | Z Phase /CLR Input (command CH0: 02h,            |     |

|    | CH1: 07h)                                        | 31  |

|    | Compare Register (command CH0: 03h, CH1: 08h).   | 32  |

|    | Digital Filter (command CH0: 04h, CH1: 09h)      | 33  |

|    | Count Value Latching (command 14h)               | 34  |

|    | Interrupt Mask (command 15h)                     | 35  |

|    | Sense Reset (command 16h)                        | 35  |

|    | Programmable Timer (command timer data: 17h,     |     |

|    | timer start: 18h)                                | 36  |

|    | One-Shot Pulse (command 19h)                     | 38  |

|    | Initialization                                   |     |

|    | Examples                                         |     |

|    | 2-Phase Pulse Count (no interrupts)              |     |

|    | 2-Phase Pulse Count (with interrupts)            | 43  |

| 5. | Using the Memory Address Map                     | .47 |

|    | Module Settings Area                             | 48  |

|    | Module Information Area                          |     |

|    | Basic Input Data Area                            |     |

|    | Basic Output Data Area                           |     |

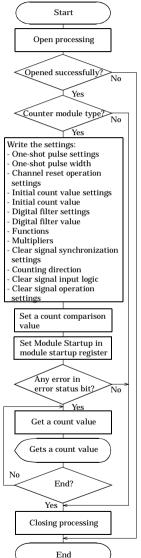

|    | Examples                                         |     |

| 6. | System Reference                                 |     |

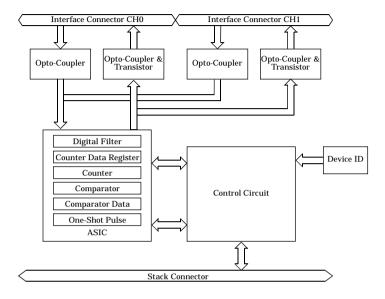

|    | Block Diagram                                    | 71  |

|    | Specifications                                   | 72  |

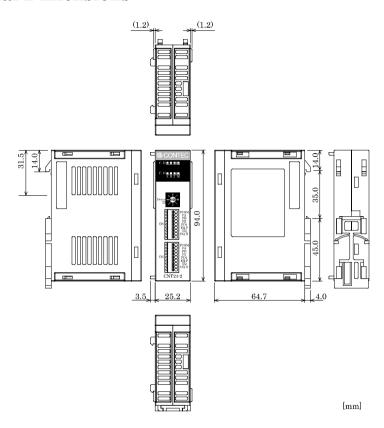

|    | External Dimensions                              |     |

|    |                                                  |     |

# 1. Introduction

Congratulations on your recent purchase of an Insulator Counter Module.

The CNT24-2(FIT)GY counts high-speed pulses so that the pulses can be processed within a F&eIT-series controller module

<CPU-CAxx(FIT)GY, CPU-SBxx(FIT)GY etc>. As such, the

CNT24-2(FIT)GY can be used for position alignment control in combination with an encoder. The insulation between external signals and the Controller Module permits the use of the Controller Module without compromising the communications features of the latter

Please read this manual carefully to create application programs and configure the system, such as setting the switches and connecting it to external devices.

#### **Features**

- -The CNT24-2(FIT)GY can perform 24-bit up and down counting covering two channels.

- -The CNT24-2(FIT)GY can count two-phase signals, such as rotary encoders and linear gauges.

- -The CNT24-2(FIT)GY is equipped with general-purpose input signals, with one point per channel.

- -A rotary switch allows you to set device IDs to help you keep track of device numbers.

- -The system incorporates a screw less connector plug that allows you to easily attach and detach wires without using any special tools.

- -Similar to other F&eIT series products, the system, in the module itself, incorporates a 35mm DIN rail mounting mechanism as a standard item. A connection to a controller module can be effected on a lateral, stack basis in a unique configuration, which permits a simple, smart system configuration without the need for a backplane board.

# Functions and control method by controller connected

The CNT24-2(FIT)GY can be connected to a variety of controllers.

Micro Controller Unit : CPU-SBxx(FIT)GY

I/O Controller Module : CPU-CAxx(FIT)GY

Monitoring & Control Server Unit : SVR-MMF2(FIT)

Monitoring & Control Server Unit : SVR-MMF(FIT)GY

Isolated Counter Module for USB :CNT24-2(USB)GY

I/O Controller Module with USB : CPU-CA10(USB)GY

The functions and control of the CNT24-2(FIT)GY vary with the controller to which the CNT24-2(FIT)GY is connected.

#### Functions available with each controller connected

|                                                                | CPU.SP | AS(ULA) CACCO | SVR-AM. | SVR.M. | CNT24.53 | CPU.CA. | J. OUS SBIC: |

|----------------------------------------------------------------|--------|---------------|---------|--------|----------|---------|--------------|

| 2-phase input; asynchronous clear; multiplication by 1/2/4     | О      | 0             |         |        | 0        | o       |              |

| 2-phase input synchronous clear, multiplication by 1/2/4       | О      | О             |         |        | o        | o       |              |

| Single-phase input, asynchronous clear,<br>multiplication by 1 | 0      | О             |         |        | o        | o       |              |

| Single-phase input with gate control,<br>multiplication by 1/2 | О      | o             | *1      | *1     | o        | o       |              |

| Digital filter                                                 | 0      | 0             |         |        | О        | O       |              |

| Interrupt function                                             | 0      |               |         |        |          |         |              |

| Programmable timer                                             | О      |               |         |        |          |         |              |

| Count match pulse output                                       | 0      | 0             |         |        | О        |         |              |

| General-purpose digital input                                  | 0      | 0             |         |        | О        | 0       |              |

| Device ID setting range                                        | 0 - 7  | 0 - 7         | 0 - 7   | 0 - 7  | 1 - 3    | 0 - 7   |              |

<sup>\*1</sup> For the function available, refer to the reference manual for the SVR-MMF2(FIT), SVR-MMF(FIT)GY.

# Control method by controller connected

|                                  |               | GPUS GR | CPUCA | SVR.Mn. | SVR.MA. | CNT24 C | $C_{PU,C_{A}}$ | TOO(CSB)CY |

|----------------------------------|---------------|---------|-------|---------|---------|---------|----------------|------------|

| Control using the I/O address ma | 0             |         |       |         |         |         |                |            |

| Control using the memory addres  | s map         |         | О     |         |         |         |                | 1          |

|                                  | FIT Protocol  |         | О     |         |         |         |                | 1          |

| Control via the Windows driver * | API-CAP(W32)  |         | 0     |         |         |         |                | 1          |

| Control via the windows driver   | API-SBP(W32)  | 0       |       |         |         |         |                | 1          |

|                                  | API-USBP(WDM) |         |       |         |         | 0       | 0              |            |

| Control over the web             |               |         | 0     | О       |         |         |                |            |

\* The API-SBP(W32) is included in the development kit DTK-SBxx(FIT)GY: the other drivers are bundled with each controller.

#### Control using the I/O address map

When connected to the CPU-SBxx(FIT)GY, the CNT24-2(FIT)GY can receive I/O instructions directly from the controller module. For details, see Chapter 4 "Using the I/O Address Map".

#### Control using the memory address map

When connected to the CPU-CAxx(FIT))GY, the CNT24-2(FIT)GY can be accessed from the host computer over the network.

The CNT24-2(FIT)GY is assigned with its device ID in the memory managed by the controller module. The application running on the host computer controls the module by reading/writing the memory managed by the controller module. For details, see Chapter 5 "Using the Memory Address Map".

#### Control via the Windows driver

For the functions and settings available when using the Windows driver, refer to the reference manual and online help for each module.

#### Control over the web

You can monitor collected data and manage the log over the web. You can use your familiar browser to easily make various settings. For details, refer to the reference manual for the SVR-MMF2(FIT), SVR-MMF(FIT)GY.

# **Limited One-Year Warranty**

CONTEC F&eIT series products are warranted by CONTEC CO., LTD. to be free from defects in material and workmanship for up to one year from the date of purchase by the original purchaser.

Repair will be free of charge only when this product is returned freight prepaid with a copy of the original invoice and a Return Merchandise Authorization to the distributor or the CONTEC group office, from which it was purchased.

This warranty is not applicable for scratches or normal wear, but only for the electronic circuitry and original products. The warranty is not applicable if the device has been tampered with or damaged through abuse, mistreatment, neglect, or unreasonable use, or if the original invoice is not included, in which case repairs will be considered beyond the warranty policy.

#### How to Obtain Service

For replacement or repair, return the device freight prepaid, with a copy of the original invoice. Please obtain a Return Merchandise Authorization Number (RMA) from the CONTEC group office where you purchased before returning any product.

\* No product will be accepted by CONTEC group without the RMA number.

#### Liability

The obligation of the warrantor is solely to repair or replace the product. In no event will the warrantor be liable for any incidental or consequential damages due to such defect or consequences that arise from inexperienced usage, misuse, or malfunction of this device.

#### **Handling Precautions**

Take the following precautions when handling this module.

- -Do not modify the module. CONTEC will bear no responsibility for any problems, etc., resulting from modifying this module.

- -Do not use or store the equipment in a hot or cold place, or in a place that is subject to severe temperature changes. (Operating temperature range: 0 50°C)

- -Do not use or store the equipment in a place subject to direct sunlight or near a heating device, such as a stove.

- -Do not use or store the equipment in a dusty or humid place. (Operating humidity range: 10 - 90%RH, No condensation)

- -As this product contains precision electronic components, do not use or store in environments subject to shock or vibration.

- Do not use or store the product near equipment generating a strong magnetic field or radio waves.

- -If you notice any strange odor or overheating, please unplug the power cord immediately.

- -In the event of an abnormal condition or malfunction, please consult the dealer from whom the equipment was purchased.

- -To avoid electric shock, please do not touch the system with a wet hand.

- -Do not open the module casing. CONTEC will disclaim any responsibility for equipment whose casing has been opened.

- -To prevent damage, please do not subject the module to impact or bend it.

- -To prevent contact malfunction, please do not touch the metallic pins on the external module connector.

- -The module contains switches that need to be properly set. Before using the module, please check its switch settings.

- -To avoid malfunction, please do not change the module switch settings in an unauthorized manner.

- -Do not operate the device module when the power for the Controller Module is on. To avoid malfunction, please be sure to turn off the power for the Controller Module.

#### FCC PART 15Class A Notice

#### NOTE

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in commercial environment.

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference at his own expense.

#### WARNING TO USER

Change or modifications not expressly approved the manufacturer can void the user's authority to operate this equipment.

#### **About the Manual**

This manual consists of the following chapters:

Chapter 1 Introduction

Chapter 2 Module Nomenclature and Settings

Explains the nomenclature of the components of the Module and their

switch settings.

Chapter 3 Connecting to an External Device

Explains interface connectors and external I/O circuits.

Chapter 4 Using the I/O Address Map

Explains I/O port bit assignments and the definitions of the bits when

the Module is used as a CPU-SBxx(FIT)GY module.

Chapter 5 Using the Memory Address Map

Explains the module settings area, the information area, and the I/O data area when the Module is used as a CPU-CAxx(FIT)GY module.

Chapter 6 System Reference

Explains module specifications and circuit block diagrams.

# 2. Module Nomenclature and Settings

# **Nomenclature of Module Components**

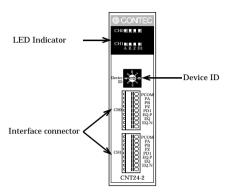

Figure 2.1. shows the names of module components. In the figure, the indicated switch settings represent factory settings.

Figure 2.1. Names of Module Components

# **Setting a Device ID**

The controller module distinguishes and keeps track of the modules that are connected to it by assigning device IDs to them.

Each module, therefore, should be assigned a unique ID.

A Device ID can be assigned in a 0 - 7 range, so that a maximum of eight modules can be distinguished.

To connect the CNT24-2(FIT)GY to the CNT24-2(USB)GY, assign a device ID between 1 and 3.

The factory setting for the Device ID is [0].

#### **Setup Method**

A Device ID can be set by turning the rotary switch that is located on the module face. A Device ID can be assigned by turning the switch.

Figure 2.2. Setting a Device ID (SW1)

# **LED Indicator**

- A: Turns on when a current flows from pin PA (low level, negative logic). (green)

- B: Turns on when a current flows from pin PB (low level, negative logic. (green)

- Z: Depends on the logic setting on the Z phase.

Z phase set to positive logic: turns on when pin PZ is open (high level, positive logic). (green)

Z phase set to negative logic: turns on when a current flows from pin PZ. (low level, negative logic).(green)

DI: turns on when a current flows from pin PD. (low level, negative logic).(green)

# 3. Connecting to an External Device

# **Interface Connector**

#### How to Connect an Interface Connector

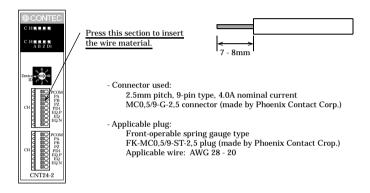

When connecting the Module to an external device, you can use the supplied connector plug. When wiring the Module, strip off approximately 7 - 8 mm of the covering for the cable, and insert the bare wire by pressing the orange button on the connector plug. Releasing the orange button after the wire is inserted to fix the cable. Compatible wires are AWG 28 - 20.

Figure 3.1. Connecting an Interface Connector and Connectors That Can

Be Used

#### Note!

Removing the connector plug by grasping the cable can break the wire.

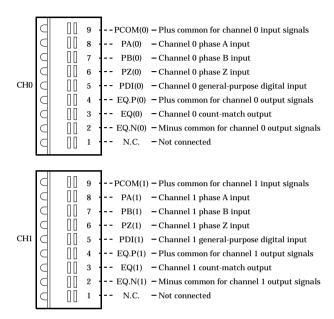

# **Signal Layout on the Interface Connector**

The Module can be connected to an external device using a 9-pin (1 group) connector that is provided on the Module face.

Figure 3.2. Signal Layout on the Interface Connector

# **Connecting an External Signal**

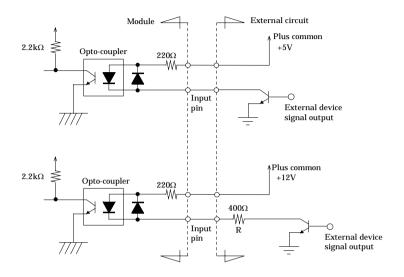

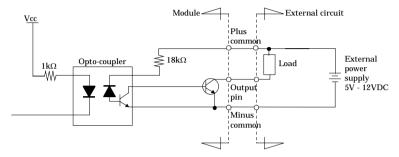

# Connecting to a Opto-Isolated Input Circuit

Figure 3.3. Isolated input Circuit and an Example of a Connection

#### Notes!

-The general-purpose input signal also has a similar circuit configuration.

-When an external power supply other than 5V is used, insert a current-limiting resistor at position R. If PV denotes an external power supply, the current-limiting resistor R can be calculated as follows:

$$\frac{P-5}{20} < Rk\Omega < \frac{P-5}{15}$$

For example, P = 12V will require the following resistance:

$350\Omega < R < 470\Omega.$

# **Output Circuit and an Example Connection**

When there is a match between a channel count and a specified value, a one-shot (one pulse) match signal is output to the outside. The signal output section has an open collector configuration based on opto-isolation. Driving the output of this module requires an external power supply.

Figure 3.4. Connecting to an Output Circuit

#### Note!

A surge voltage protection circuit is not provided on the output transistors for this Module. Therefore, when driving relays, lamps, and other induction loads using this Module, a surge voltage countermeasure should be provided on the load side.

For a description of how to deal with surge voltages, see "Surge Voltage Countermeasures".

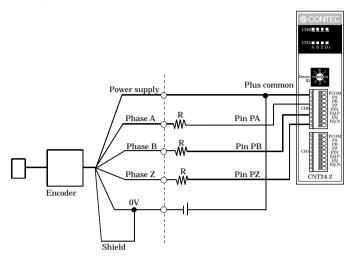

# **Connecting to a Rotary Encoder**

<sup>\*</sup> A  $400\Omega$  resistor is required at position R when used at 12V, but not at 5V.

Figure 3.5. Connecting to a Rotary Encoder

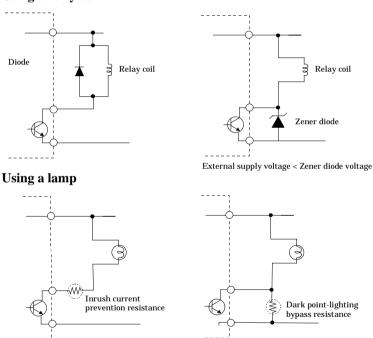

# **Surge Voltage Countermeasures**

When connecting a load that generates surge voltages and inrush currents, such as an induction load (relay coil) or an incandescent light bulb, to the one-shot pulse output, appropriate protection must be provided in order to prevent damage to the output stage or a malfunction due to noise. The rapid shutoff of a coil, such as a relay, generates a sudden high-voltage pulse. If this voltage exceeds the voltage tolerance level of the output transistor, it can cause the transistor to gradually deteriorate, or even completely damage the transistor. Therefore, when driving an induction load, such as a relay coil, you should always connect a surge-absorbing device. The following illustrates a surge voltage countermeasure that can be employed:

#### Using a relay coil

Figure 3.6. Surge Voltage Countermeasure

#### Note!

In order for a protection circuit to operate effectively, it must be connected within 50 cm of a load and a contact point.

# 4. Using the I/O Address Map

# **Starting I/O Address**

When connected to a CPU-SBxx(FIT)GY, the CNT24-2(FIT)GY can directly receive I/O commands from the controller module. Depending on how the Device ID is set, the I/O addresses indicated below will be used exclusively by the CNT24-2(FIT)GY.

Because the address bus on which the I/O address space is specified is not fully decoded in continued 16 bits, four starting I/O addresses exist in each Device ID.

If the Device ID is set to 0h, one of the four addresses (0800h, 0840h, 0880h, or 08C0h) will be used as a starting I/O address.

Table 4.1. List of Starting I/O Addresses

| ID No. |                          | lress         |               |               |

|--------|--------------------------|---------------|---------------|---------------|

| 0      | 0800h - 081Fh(recommend) | 0840h - 085Fh | 0880h - 089Fh | 08C0h - 08DFh |

| 1      | 1800h - 181Fh(recommend) | 1840h - 185Fh | 1880h - 189Fh | 18C0h - 18DFh |

| 2      | 2800h - 281Fh(recommend) | 2840h - 285Fh | 2880h - 289Fh | 28C0h - 28DFh |

| 3      | 3800h - 381Fh(recommend) | 3840h - 385Fh | 3880h - 389Fh | 38C0h - 38DFh |

| 4      | 4800h - 481Fh(recommend) | 4840h - 485Fh | 4880h - 489Fh | 48C0h - 48DFh |

| 5      | 5800h - 581Fh(recommend) | 5840h - 585Fh | 5880h - 589Fh | 58C0h - 58DFh |

| 6      | 6800h - 681Fh(recommend) | 6840h - 685Fh | 6880h - 689Fh | 68C0h - 68DFh |

| 7      | 7800h - 781Fh(recommend) | 7840h - 785Fh | 7880h - 789Fh | 78C0h - 78DFh |

For detailed specifications on the I/O space that is controlled by the controller module, see the controller module manual.

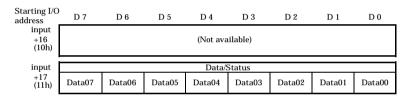

# **List of I/O Address Maps**

#### **Input Port**

Figure 4.1. Input Port

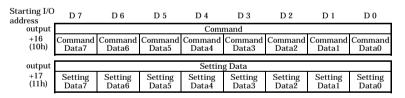

#### **Output Port** D 6 $D_{0}$ D 5 D 4 D 3 D 2 D 1 Starting I/O address +0 (00h) (Not allowed) +1 (01h) Interrupt Data +2 (02h) IRQ9 Data IRQ7 Data IRQ5 Enable N/A N/A N/A N/A Data +3 (03h) : (Not allowed) +15 (0Fh) Command +16 (10h) Command Command Command Command Command Command Command Data6 Data5 Data4 Data3 Data2 Data1 Data0 Command Data7 Data3 Setting Data Setting Data7 Setting Data6 Setting Data5 Setting Data4 Setting Data3 Setting Data2 Setting Data1 Setting Data0 +17 (11h) +18 (12h) (Not allowed)

Figure 4.2. Output Port

+31 (1Fh)

17

# **Specifications Common to F&eIT Products**

The starting I/O addresses from +0h - +Fh are common to all modules in the F&eIT series.

#### **Product Information**

| Starting I/O<br>address | D 7               | D 6     | D 5      | D 4 | D 3               | D 2               | D 1               | D 0               |  |  |  |  |

|-------------------------|-------------------|---------|----------|-----|-------------------|-------------------|-------------------|-------------------|--|--|--|--|

| input                   |                   | Product | Category |     | Revision Data     |                   |                   |                   |  |  |  |  |

| +0<br>(00h)             | 0                 | 0       | 1        | 1   | Revision<br>Data3 | Revision<br>Data2 | Revision<br>Data1 | Revision<br>Data0 |  |  |  |  |

|                         | Product ID Number |         |          |     |                   |                   |                   |                   |  |  |  |  |

| +1<br>(01h)             | 0                 | 0       | 0        | 0   | 0                 | 0                 | 0                 | 0                 |  |  |  |  |

Figure 4.3. Product Information

-Revision Data [D3 - D0]:

This is product update information, subject to change without notice, that is controlled by Contec.

-Product Category [D7 - D4]:

This is a module function classification code.

For the CNT24-2(FIT)GY, the code is "3h".

| Code | Function             |

|------|----------------------|

| 0    | Extention BUS        |

| 1    | Digital input-output |

| 2    | Analog input-output  |

| 3    | Counter              |

| 4    | Serial communication |

| 5    | GPIB                 |

| 6-F  | Reserved             |

Figure 4.4. Product Category

-Product ID Number [D7 - D0]:

This is a product ID number within the same Product ID Number.

For the CNT24-2(FIT)GY, the ID is "0h".

Following are examples demonstrate the initialization of the device by high-level languages:

#### Microsoft C

#### Microsoft OBASIC

\* ADR indicates the starting I/O address for the module.

#### **Interrupt Status**

This is a port on which the interrupt status generated by the Module can be verified.

Although in this example values are assigned centered on the status concerning

interrupt levels, information on interrupt sources varies from module to module.

| Starting I/O address   | D 7    | D 6    | D 5 | D 4 | D 3 | D 2  | D 1  | D 0  |

|------------------------|--------|--------|-----|-----|-----|------|------|------|

| input Interrupt Status |        |        |     |     |     |      |      |      |

| +2<br>(02h)            | Enable | Status | 0   | 0   | 0   | IRQ9 | IRQ7 | IRQ5 |

#### Figure 4.5. Interrupt Status

-Enable [D7]:

This verifies the interrupt source enabled/disabled status.

The value "1" indicates that a hardware interrupt on the controller module is enabled.

-Status [D6]:

This bit indicates an interrupt request status in the module.

When IRQ5, IRQ7, or IRQ9 is "1", this bit will also be "1".

-IRO\* [D2 - D0]:

These bits allow you to verify the interrupt level that is currently set. The current interrupt level is indicated as "1".

Following are examples of the initialization that is performed in high-level languages:

# Microsoft C IrqStatus = inp( ADR+2 ); IrqStatus = INP( ADR+2 )

#### **Setting an Interrupt Level**

| Starting I/O<br>address | D 7    | D 6 | D 5 | D 4      | D 3     | D 2          | D 1          | D 0          |

|-------------------------|--------|-----|-----|----------|---------|--------------|--------------|--------------|

| output                  |        |     |     | Interruj | pt Data |              |              |              |

| +2<br>(02h)             | Enable | N/A | N/A | N/A      | N/A     | IRQ9<br>Data | IRQ7<br>Data | IRQ5<br>Data |

#### Figure 4.6. Setting an Interrupt Level

-Enable [D7]:

This bit enables an interrupt source.

-IRQ\* [D2 - D0]:

The interrupt level used by the module is set in these bits.

Following are examples of initialization settings that can be affected in high-level languages.

The interrupt level to be used is assigned to IRQ5.

| Microsoft C   |         | Microsoft QBASIC |

|---------------|---------|------------------|

| outp ( ADR+2. | 0x81 ): | OUT ADR+2, &H81  |

# **Bit Assignments for I/O Ports**

The I/O ports for the counting function have command-section and data-section registers.

A register can be set as follows: First, a command is issued (OUT) to a port located at *starting I/O address* + 16 to make the register available for setting. For output, data is assigned (OUT) to the register at port +17; for input, the +17 port is read. In other words, for both input and output, a command is issued (OUT) to the output port +16 to make registers available for setting, and either data is issued (OUT) to the port +17 to set the register or the register is read at the +17 port.

When setting a register even when using the same command, the command should be output to the output port +16 each time.

Figures 6.7. and 6.8. show I/O port bit assignments.

Figure 4.7. Input Port

Figure 4.8. Output Port

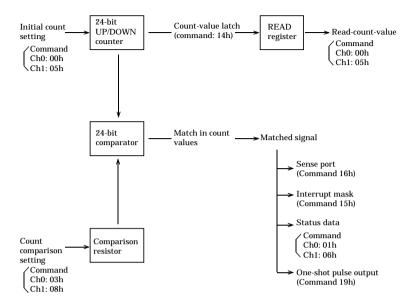

# Flow of Count Values

Figure 4.9. Flow of Count Values

# **Operation Commands**

**Table 4.2. Output Commands**

| Command<br>(h) | D7    | D6      | D5       | D4        | D3      | D2                         | D1     | D0    | Function                   | Data<br>size |

|----------------|-------|---------|----------|-----------|---------|----------------------------|--------|-------|----------------------------|--------------|

| 00             |       |         | CH       | 0 initial |         | CH0 initial count value    | 24-bit |       |                            |              |

| 01             | RESET | SEL     | ZSEL     | UD/AB     | DIR     | SEL2                       | SEL1   | SEL0  | CH0 mode setting           | 8-bit        |

| 02             |       | No      | ot allow | ed        |         | ZE1                        | ZE0    | 0     | CH0 phase Z CLR input      | 3-bit        |

| 03             |       |         | CH0 c    | ount cor  |         | CH0 count comparison value | 24-bit |       |                            |              |

| 04             |       | Not al  | lowed    |           |         | CH0 digital filter         | 4-bit  |       |                            |              |

| 05             |       |         |          | Same a    | as CH0  |                            |        |       | CH1 initial count value    | 24-bit       |

| 06             |       |         |          | Same a    | as CH0  |                            |        |       | CH1 mode setting           | 8-bit        |

| 07             |       |         |          | Same a    | as CH0  |                            |        |       | CH1 phase Z CLR input      | 3-bit        |

| 08             |       |         |          | Same a    | as CH0  |                            |        |       | CH1 count comparison value | 24-bit       |

| 09             |       |         |          | Same a    | as CH0  |                            |        |       | CH1 digital filter         | 4-bit        |

| 14             |       |         | Not al   | lowed     |         |                            | CH1LT  | CH0LT | Count-value latch          | 2-bit        |

| 15             | No    | t allow | ed       | TIME      | Not a   | llowed                     | CH1    | CH0   | Interrupt mask             | 3-bit        |

| 16             | No    | t allow | ed       | TIME      | Not a   | llowed                     | CH1    | CH0   | Sense reset                | 3-bit        |

| 17             |       | P       | rogram   | mable ti  |         | Timer data                 | 8-bit  |       |                            |              |

| 18             |       |         | N        | ot allow  | START   | Timer start                | 1-bit  |       |                            |              |

| 19             |       |         | One-     | shot pul  | se widt | h data                     |        |       | One-shot pulse             | 8-bit        |

**Table 4.3. Input Commands**

| Command<br>(h) | D7       | D6 | D5 | D4        | D3      | D2              | D1     | D0  | Function        | Data<br>size |

|----------------|----------|----|----|-----------|---------|-----------------|--------|-----|-----------------|--------------|

| 00             |          |    | CH | 0 initial |         | CH0 count value | 24-bit |     |                 |              |

| 01             | AI       | Z  | Α  | В         | 1       | U/D             | EQ     | U   | CH0 status      | 8-bit        |

| 02             |          |    | CH | 1 initial | count v | alue            |        |     | CH1 count value | 24-bit       |

| 03             | AI Z A B |    |    |           | 1       | U/D             | EQ     | U   | CH1 status      | 8-bit        |

| 15             | 0        | 0  | 0  | TIME      | 0       | 0               | CH1    | CH0 | Interrupt mask  | 3-bit        |

| 16             | 0        | 0  | 0  | TIME      | 0       | 0               | CH1    | CH0 | SensePort       | 3-bit        |

# **Description of Input Commands**

# Reading a Count (command CH0: 00h, CH1: 05h)

By reading the contents of the READ register for a corresponding channel, this command reads a count value. By issuing the command to the output port +16 and reading the input port +17 three times, you can read low, middle, and high count values.

In the initial state, the contents of the READ register are undefined.

Following are programs that read a count value from CH0:

#### Microsoft C

#### Microsoft OBASIC

```

outp( ADR+16, 0x0 );

LowerData = inp( ADR+17 );

MiddleData = inp( ADR+17 );

UpperData = inp( ADR+17 );

UpperData = inp( ADR+17 );

UpperData = INP( ADR+17 )

OUT ADR+16, &HO

LowerData = INP( ADR+17 )

MiddleData = INP( ADR+17 )

```

In this case, the count value latch for CH0 must be pre-set to [1].

#### Status Data (command CH0: 01h, CH1: 06h)

| Starting I/O<br>address | D7 | D6 | D5 | D4 | D3 | D2  | D1                       | D0 |

|-------------------------|----|----|----|----|----|-----|--------------------------|----|

| 01h/06h                 | AI | Z  | Α  | В  | 1  | U/D | $\overline{\mathrm{EQ}}$ | U  |

By issuing the command to the output port +16 and reading the input port +17, you can monitor signal inputs, the direction of counting, any count matches, and the state of any abnormal input.

- AI When phases A and B change simultaneously during two-phase input or simultaneous changes in UP and DOWN pulses are detected during UP/DOWN input, the event is flagged as abnormal pulse input, and this bit is set to [1].

- 1: Abnormal input detected

- 0: No abnormal input detected

- Z Indicates the input status of phase Z.

<Positive logic>

1: Phase Z input status [1]

0: Phase Z input status [0]

<Negative logic>

1: Phase Z input status [0]

0: Phase Z input status [1]

A Indicates the input status of phase A.

1: Phase A input status [1]

0: Phase A input status [0]

B Indicates the input status of phase B.

1: Phase B input status [1]

0: Phase B input status [0]

U/D Count direction operating status

This status bit indicates the counting direction of the current UP/DOWN counter.

0: Counting in UP direction

1: Counting in DOWN direction

- EQ Match detection output

- 0: Count value matches the contents of the compare register.

- 1: Count value does not match the contents of the compare register

- U Indicates the status of generic input

1: Generic input status [1]

0: Generic input status [0]

#### Notes!

- The initial state changes with the external connection state.

- The status for phases A, B, and Z represents the data that is in effect after the filtering function is processed, and thus involves a delay of 4 setting cycle clocks. The generic input indicates the state of external input "as is".

- The logic for phase Z is set in [ZSEL] in the operating mode settings.

#### **Interrupt Mask (command 15h)**

| Starting I/O address | D7 | D6 | D5 | D4   | D3 | D2 | D1  | D0  |

|----------------------|----|----|----|------|----|----|-----|-----|

| 15h                  | 0  | 0  | 0  | TIME | 0  | 0  | CH1 | CH0 |

This command allows you to monitor the status of the current interrupt mask that was set using the interrupt mask command. TIME is associated with the programmable timer, and CH1 - CH0 are associated with channels. When these bits are [1], the interrupt is masked, and no interrupt signals are output.

You can monitor the masking status by issuing the value 15h to the output port +16 and by reading the input port +17.

0: Not masked

1: Masked

Note!

Initial state: 1FH

#### Sense Port (command 16h)

| Starting I/O<br>address | D7 | D6 | D5 | D4   | D3 | D2 | D1  | D0  |

|-------------------------|----|----|----|------|----|----|-----|-----|

| 16h                     | 0  | 0  | 0  | TIME | 0  | 0  | CH1 | CH0 |

This command indicates any matching counts in the channels and any time-up status.

You can monitor the status of the sense port by issuing the value 16h to the output port +16 and reading the input port +17.

-TIME This bit is set to [1] when the time limit that is set on the programmable timer has elapsed.

-CH1 - CH0

With regard to channels CH1 - CH0, when there is a match between the contents of the UP/DOWN counter and the compare register, the bits associated with the channels become [1]. In this manner, when counting operations are performed on multiple channels and an interrupt is generated upon the generation of a match signal, you can determine from which channel the interrupt is generated.

0: No match in counts; pending time-up

1: A match in counts; time-up

Notes!

- Initial state: 00h

- If an interrupt is generated with the interrupt option set, and if one of the bits in TIME or CH1 to CH0 is set to [1], before another interrupt can be generated, the affected sense bit must be reset. For a description of how to reset a sense bit, see "Sense Reset" on output ports.

# **Description of Output Commands**

#### **Initial Count Value (command CH0: 00h, CH1: 05h)**

The command is issued to the output port +16, and an initial count value is set on the output port +17. Because count data consists of 24 bits, count values are output three times in low, middle, and high order, 8 bits each time. When the third (high 8 bits) count value is output, data consisting of 24 bits is loaded simultaneously by the counting process.

Following are program examples that set a count value 100(64h) on CH0:

# Microsoft C Microsoft QBASIC outp( ADR+16, 0x0 ); outp( ADR+17, 0x64 ); outp( ADR+17, 0x64 ); outp( ADR+17, 0x0 ); outp( ADR+17, &H0 outp( ADR+17, 0x0 ); outp( ADR+17, &H0 outp( ADR+17, &H

# Operating Mode (command CH0: 01h, CH1: 06h)

| Starting I/C<br>address | D7    | D6  | D5   | D4                 | D3  | D2   | D1   | D0   |

|-------------------------|-------|-----|------|--------------------|-----|------|------|------|

| 01h/06h                 | RESET | SEL | ZSEL | $UD/\overline{AB}$ | DIR | SEL2 | SEL1 | SEL0 |

The command is issued to the output port +16, and the operating mode is set on the output port +17.

RESET Clears the 24-bit UP/DOWN counter to "000000h".

No counting is performed during the period RESET = 0.

0: Counter cleared 1: Counting

After a zero-clear operation is performed when Z-phase input is enabled one time, and when a RESET =0 operation is performed, the "Z-phase enabled one time" option is set again.

SEL Switches pulse inputs into counters.

0: Opto-isolated input (fixed)

1: Not available

ZSEL Selects Z-phase input logic (positive/negative).

0: Positive logic (HIGH active)

1: Negative logic (LOW active)

UD/AB, SEL2 to 0

Selects a counter operation mode.

**Table 4.4. Counter Operation Mode**

| UD/AB | DIR   | SEL2 | SEL1 | SEL0 | Operating mode to be set                                  |

|-------|-------|------|------|------|-----------------------------------------------------------|

| 0     |       | 0    | 0    | 0    | 2-phase input, synch clear, 1x mode                       |

| 0     |       | 0    | 0    | 1    | 2-phase input, synch clear, 2x mode                       |

| 0     |       | 0    | 1    | 0    | 2-phase input, synch clear, 4 mode                        |

| 0     | See   | 1    | 0    | 0    | 2-phase input, asynch clear, 1x mode                      |

| 0     | Table | 1    | 0    | 1    | 2-phase input, asynch clear, 2x mode                      |

| 0     | 6.5.  | 1    | 1    | 0    | 2-phase input, asynch clear, 4 mode                       |

| 1     |       | 0    | 1    | 1    | mono-phase input, synch clear, 1x mode                    |

| 0     |       | 0    | 1    | 1    | Mono-phase input with gate control, asynch clear, 1x mode |

| 0     |       | 1    | 1    | 1    | Mono-phase input with gate control, asynch clear, 2x mode |

DIR Switches the counting directions of the rotary encoder.

**Table 4.5. Switching Counting Directions**

| DIR | Direction of rotation of rotary encoder |                  |  |  |  |  |  |  |

|-----|-----------------------------------------|------------------|--|--|--|--|--|--|

| DIK | Clockwise                               | Counterclockwise |  |  |  |  |  |  |

| 0   | DOWN                                    | UP               |  |  |  |  |  |  |

| 1   | UP                                      | DOWN             |  |  |  |  |  |  |

Note!

Initial state: 00h for all channels

# **Counter Operating Modes**

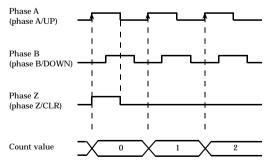

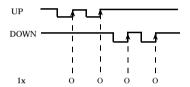

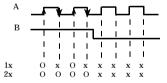

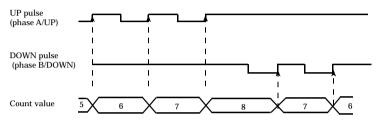

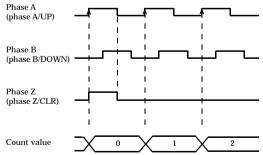

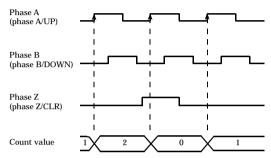

#### 2-Phase Input

2-phase pulse input refers to the input of two pulses, A phase  $\,$

(fast signal) and B phase (slow signal) that differ in phase by 90°. If Z phase is provided (reference position signal), the counter can be cleared using 2-phase pulse input.

$<sup>^{*}</sup>$  The figure above illustrates the counting operation when DIR = 1 is specified. If DIR = 0, a DOWN count commences when phase A rises.

Figure 4.10. Example of Counting with 2-Phase Input

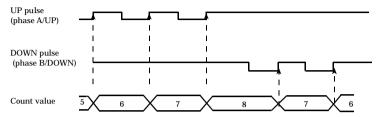

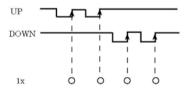

#### Mono-phase input

During mono-phase input, the system counts up upon the input of an UP pulse, and counts down upon the input of a DOWN pulse. A count fails if UP and DOWN pulses occur simultaneously or both pulses happen to be LOW.

<sup>\*</sup> The figure above illustrates the counting operation when DIR = 1 is specified. If DIR = 0, a DOWN count commences when a phase A pulse rises, and an UP count commences when a phase B pulse falls.

Figure 4.11. Example of Counting with Mono-Phase Input

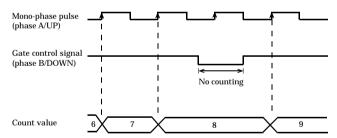

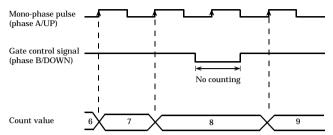

#### Mono-Phase Input with Gate Control

The counter can be started/stopped according to the gate control signal that is input together with a string of mono-phase pulses. The clear signal zero-clears the counter value.

<sup>\*</sup> The figure above illustrates the counting operation when DIR = 1 is specified. If DIR = 0, a DOWN count commences when the gate control signal (phase B/DOWN) is HIGH and when a mono-phase pulse example (phase A/UP) rises; the counting stops when the gate control signal is LOW.

Figure 4.12. Example of a Mono-Phase Input Count with Gate Control

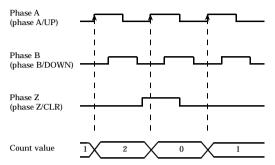

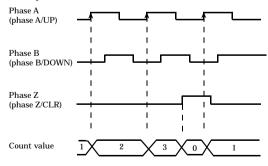

#### Synchronous Clear

If DIR=1 and ZSEL=0, the counter is zero-cleared when A phase rises with the B-phase input LOW and the Z-phase input HIGH; the counting process is started when A phase rises after the Z-phase input turns LOW.

<sup>\*</sup> If DIR = 0, a DOWN count commences when phase A rises with phase B LOW. if ZSEL= 1, the operation is enabled when phase Z input is LOW.

Figure 4.13. Example of Counting with a Synchronous Clear

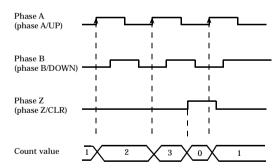

#### Asynchronous Clear

If DIR=1 and ZSEL=0, the counter is zero-cleared when Z phase turns HIGH, irrespective of the input state of phase A or B. The counting process is started at the next rise of A phase, irrespective of the input state of Z phase.

<sup>\*</sup> If DIR = 0, a DOWN count commences when phase A rises with phase B LOW. if ZSEL= 1, the operation is enabled when phase Z input is LOW.

Figure 4.14. Example of Counting with an Asynchronous Clear

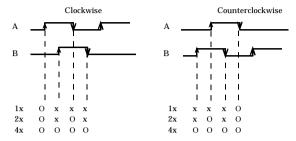

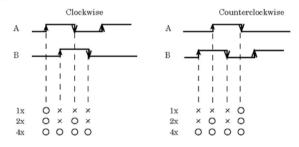

#### **Count Input Multiplier**

Detailed control can be effected by setting the count input multiplier to 2 or 4.

#### - 2-phase input

#### - Mono-phase input

Mono-phase input only requires the 1x mode setting. Settings 2x or greater are not recognized.

#### - Mono-phase input with gate control

Figure 4.15. Example of Counting with a Count Input Multiplier Set

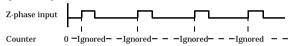

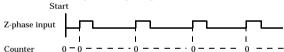

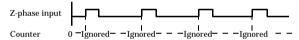

# Z Phase /CLR Input (command CH0: 02h, CH1: 07h)

| Starting I/O<br>address | D7 | D6 | D5      | D4 | D3 | D2  | D1  | D0 |   |

|-------------------------|----|----|---------|----|----|-----|-----|----|---|

| 02h/07h                 |    |    | Not use | d  |    | ZE1 | ZE0 | 0  | 1 |

The command is issued to the output port +16, and the number of Z-phase input operations is assigned to the output port +17.

ZE1, ZE0 Selecting a Z phase input mode

Table 4.6. Z phase Input Mode

|   | ZE1 | ZE0 | Specified state                                                  |

|---|-----|-----|------------------------------------------------------------------|

|   | 0   | 1   | Z-phase input disabled. Use this value when there is no Z phase. |

| * | 1   | 0   | Enabled only for one-time input of the next Z phase.             |

|   | 1   | 1   | Enabled for all Z-phase input operations.                        |

<sup>\*</sup> When in the initial condition

- Z-phase input disabled (ZE1=0, ZE0=1)

- Enabled only for one-time input of the next Z phase (ZE1=1, ZE0=0)  $\,$

- Enabled for all Z-phase input operations (ZE1=1, ZE0=1)

Figure 4.16. Effective Z Phase Count ZSEL=0 (Positive Logic)

#### Notes!

- The initial setting is "effective for only one input of the next Z phase" (04h).

- If ZSEL=1 (negative logic), the Z phase input is effective only when it is LOW.

- If the Z phase /CLR input command is not used, the following settings must be specified: ZE1=0, ZE0=1 (Z phase input disabled).

- -When the Z phase input is effective only once and if a zero-clear is performed upon the input of Z phase and the count value is cleared by setting RESET=0, the "Z-phase effective one time" setting is effected again when RESET=0 is set.

## Compare Register (command CH0: 03h, CH1: 08h)

This command compares the count value for a corresponding channel with the value of a compare register, and if there is a match, the command sets  $\overline{EQ}$ " for the status bit to "0" (the "0" value remains in effect for the duration of the match). The initial condition for this register is 0h. The command is issued to the output port +16, and a count comparison value is set on the output port +17. Because the count comparison value is 24-bit long, the data is output three times, in low, middle, and high order. Following are example programs that assigns a count comparison value 1000 (3E8h) to channel CH1:

#### Microsoft C

#### Microsoft OBASIC

```

outp( ADR+16, 0x3 );

OUT ADR+16, &H3

outp( ADR+17, 0xe8 );

OUT ADR+17, &HE8

outp( ADR+17, 0x3 );

OUT ADR+17, &H3

outp( ADR+17, 0x0 );

OUT ADR+17, &H3

```

Depending on the settings, a once-shot pulse can also be output to an external device (see the section on One-Shot Pulse).

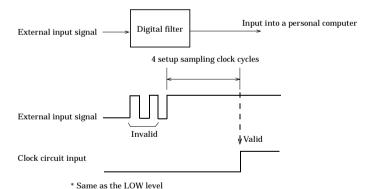

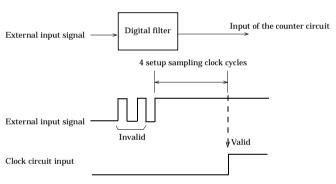

## Digital Filter (command CH0: 04h, CH1: 09h)

| Starting I/O<br>address | D7 | D6 | D5     | D4 | D3    | D2       | D1        | D0    |

|-------------------------|----|----|--------|----|-------|----------|-----------|-------|

| 04h/09h                 |    | No | t used |    | Clock | data for | digital f | ilter |

The digital filter is designed to ensure that the counter will operate normally even in the presence of noise in the pulse input to the counter and in phase A, B, and Z signals. Digital filter clock setting data determines the sampling clock cycle for the digital filter.

When detecting 4 clocks of continuous HIGH (or LOW) signals by sampling the input signals with this sampling clock, the digital filter outputs a HIGH (or a LOW), and transmits the signal to the counter circuit.

The command is issued to the output port +16, and a sampling cycle is set on the output port +17. The allowable range is 0.1sec - 1056.1sec.

Notice that because all external input signals (with the exception of general-purpose input signals) are directed into the internal counter through the digital filter, they are read with a delay of 4 sampling clock cycles.

In the initial condition, external input signals are read with a delay of 0.4sec.

Figure 4.17. Digital Filter

Table 4.7. Setting a Digital Filter Clock

| D3 | D2 | D1 | D0 | Digital filter<br>clock cycle | Input frequency     |

|----|----|----|----|-------------------------------|---------------------|

| 0  | 0  | 0  | 0  | 0.1µsec                       | Approx. 1MHz max.   |

| 0  | 0  | 0  | 1  | 6.5µsec                       | Approx. 15kHz max.  |

| 0  | 0  | 1  | 0  | 25.7μsec                      | Approx. 3.5kHz max. |

| 0  | 0  | 1  | 1  | 32.1µsec                      | Approx. 3kHz max.   |

| 0  | 1  | 0  | 0  | 204.9μsec                     | Approx. 480Hz max.  |

| 0  | 1  | 0  | 1  | 211.3µsec                     | Approx. 470Hz max.  |

| 0  | 1  | 1  | 0  | 230.5µsec                     | Approx. 430Hz max.  |

| 0  | 1  | 1  | 1  | 236.9µsec                     | Approx. 420Hz max.  |

| 1  | 0  | 0  | 0  | 819.3µsec                     | Approx. 122Hz max.  |

| 1  | 0  | 0  | 1  | 825.7µsec                     | Approx. 121Hz max.  |

| 1  | 0  | 1  | 0  | 844.9µsec                     | Approx. 118Hz max.  |

| 1  | 0  | 1  | 1  | 851.3μsec                     | Approx. 117Hz max.  |

| 1  | 1  | 0  | 0  | 1024.1μsec                    | Approx. 97Hz max.   |

| 1  | 1  | 0  | 1  | 1030.5μsec                    | Approx. 96Hz max.   |

| 1  | 1  | 1  | 0  | 1049.7μsec                    | Approx. 95Hz max.   |

| 1  | 1  | 1  | 1  | 1056.1μsec                    | Approx. 94Hz max.   |

Precision is approximately ±1/10000 relative to a cycle setting.

#### Notes!

- In the initial condition, the clock is set at 0.1 µsec (which is the default).

- Some noise signals can cause a delay greater than 4 clock cycles.

- Any change in level occurring at a frequency faster than a set sampling clock cycle is invalidated and the level is not correctly counted. Therefore, signals less than the input frequency must be entered.

## **Count Value Latching (command 14h)**

| Starting I/O<br>address | D7 | D6 | D5 | D4     | D3 | D2 | D1     | D0     |

|-------------------------|----|----|----|--------|----|----|--------|--------|

| 14h                     |    |    | No | t used |    |    | CH1 LT | CH0 LT |

This command latches a count value on a corresponding channel to the READ register. The command issues the value "14h" to the output port +16, and sets a data latch on the output port +17. The command latches the count value by setting the applicable bit to "1". All channels can be latched simultaneously by setting all applicable bits to "1".

#### Note!

The initial condition is no-latch (00h).

### **Interrupt Mask (command 15h)**

| Starting I/O<br>address | D7 | D6       | D5 | D4   | D3  | D2   | D1  | D0  |

|-------------------------|----|----------|----|------|-----|------|-----|-----|

| 15h                     |    | Not used |    | TIME | Not | used | CH1 | CH0 |

This command issues the value "15h" to the output port +16, and sets a mask on the output port +17. The generation of interrupt signals is disabled when an applicable bit is set to "1".

TIME

Setting the value "1" disables any interrupt after the time that is set on the programmable timer has elapsed. Setting the value "0" resets the disabled condition.

#### CH1 to CH0

These bits are associated with the respective channels. Setting the value "1" to any of these bits disables a count-match interrupt on the associated channel. Setting the value "0" resets the disabled condition.

#### Notes!

- In the initial condition, all channels are timer-masked (1Fh).

- Even in the masked state, on all channels the count match and the timer-up conditions change.

## Sense Reset (command 16h)

| Starting I/O<br>address | D7 | D6       | D5 | D4   | D3  | D2   | D1  | D0  |   |

|-------------------------|----|----------|----|------|-----|------|-----|-----|---|

| 16h                     |    | Not used |    | TIME | Not | used | CH1 | CH0 | 1 |

The interrupt sense sets an applicable bit to "1" when a count-match or timer-up condition is detected on a given channel. When the applicable bit is "1", an interrupt signal is not generated when another count-match or timer-up condition arises. Issuing the value "+16h" to the output port +16 and the value "1" to the applicable bit on the output port clears the sense bit, and enables the generation of another interrupt signal.

TIME Sets the sense bit when the programmable timer is up.

CH1 to CH0

Resets the sense bit when counts match on the respective channels.

## **Programmable Timer**

## (command timer data: 17h, timer start: 18h)

| Starting I/O address | D7       | D6 | D5      | D4        | D3        | D2        | D1 | D0 |  |  |

|----------------------|----------|----|---------|-----------|-----------|-----------|----|----|--|--|

| 17h                  |          | P  | rogramı | nable tir | ner setti | ings data | ì  |    |  |  |

| •                    |          |    |         |           |           |           |    |    |  |  |

|                      | D7       | D6 | D5      | D4        | D3        | D2        | D1 | D0 |  |  |

| 18h                  | Not used |    |         |           |           |           |    |    |  |  |

The programmable timer can generate interrupts in cycles that are compatible with 32-bit settings data. To operate the timer, you need to set 32-bit data and assign the value "1" to the START bit.

The programmable timer can be set by issuing the value "17h" to the output port +16, and by setting timer data on the output port +17. Because it is 32-bit long, the timer data must be set 8 bits at a time sequentially from the lowest bit, for a total of 4 times. The allowable range is 1 msec - 200 sec.

The timer starts when the timer start command "18h" is issued to the output port +16, and the applicable bit is set to "1" on the output port +17; setting this bit to "0" stops the timer.

Table 4.8. shows the relationship between programmable timer setup data and timer interrupt cycles. Following are example programs that set the programmable timer to 1 sec.

#### Microsoft C

#### Microsoft OBASIC

| outp ( ADR+16, 0x1<br>outp ( ADR+17, 0x1<br>outp ( ADR+17, 0x2<br>outp ( ADR+17, 0x2<br>outp ( ADR+17, 0x3<br>outp ( ADR+16, 0x1<br>outp ( ADR+16, 0x1<br>outp ( ADR+17, 0x1 | 2c ); OUT<br>31 ); OUT<br>1 ); OUT<br>18 ); OUT | ADR+16,<br>ADR+17,<br>ADR+17,<br>ADR+17,<br>ADR+17,<br>ADR+16,<br>ADR+16, | &HFF<br>&H2C<br>&H31<br>&H1<br>&H18 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

#### Note!

In the initial condition, the timer is stopped.

Table 4.8. Relationship between Programmable Timer Setup

Data and Interrupt Cycles

$$\frac{\text{[timer data]} \times 50 + 50) \times 10^{-6} = \text{time interrupt cycle [msec]}}{\downarrow}$$

32-bit (converted into decimal)

|      | Progra | nmal            |   | Timer interrupt |               |     |      |         |

|------|--------|-----------------|---|-----------------|---------------|-----|------|---------|

| High | byte   | <del>&lt;</del> |   |                 | $\rightarrow$ | Low | byte | cycle   |

| 0    | 0      | 0               | 0 | 4               | E             | 1   | F    | 1msec   |

| 0    | 0      | 0               | 3 | 0               | D             | 3   | F    | 10msec  |

| 0    | 0      | 1               | E | 8               | 4             | 7   | F    | 100msec |

| 0    | 1      | 3               | 1 | 2               | С             | F   | F    | 1sec    |

| 0    | 2      | 6               | 2 | 5               | 9             | F   | F    | 2sec    |

| 0    | 3      | 9               | 3 | 8               | 6             | F   | F    | 3sec    |

| 0    | 4      | С               | 4 | В               | 3             | F   | F    | 4sec    |

| 0    | 5      | F               | 5 | E               | 0             | F   | F    | 5sec    |

| 0    | 7      | 2               | 7 | 0               | D             | F   | F    | 6sec    |

| 0    | 8      | 5               | 8 | 3               | Α             | F   | F    | 7sec    |

| 0    | 9      | 8               | 9 | 6               | 7             | F   | F    | 8sec    |

| 0    | A      | В               | A | 9               | 4             | F   | F    | 9sec    |

| 0    | В      | E               | В | С               | 1             | F   | F    | 10sec   |

| 1    | 1      | Е               | 1 | A               | 2             | F   | F    | 15sec   |

| 1    | 7      | D               | 7 | 8               | 3             | F   | F    | 20sec   |

| 2    | 3      | С               | 3 | 4               | 5             | F   | F    | 30sec   |

| 2    | F      | A               | F | 0               | 7             | F   | F    | 40sec   |

| 3    | В      | 9               | A | С               | 9             | F   | F    | 50sec   |

| 7    | 7      | 3               | 5 | 9               | 3             | F   | F    | 100sec  |

| В    | 2      | D               | 0 | 5               | D             | F   | F    | 150sec  |

| E    | Е      | 6               | В | 2               | 7             | F   | F    | 200sec  |

Precision is approximately  $\pm 1/10000$  relative to a cycle setting

## **One-Shot Pulse (command 19h)**

| Starting I/O<br>address | D7                        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|-------------------------|---------------------------|----|----|----|----|----|----|----|--|

| 19h                     | One-shot pulse width data |    |    |    |    |    |    |    |  |

When there is a match between a count value on a channel and a count compare value, a one-shot pulse is output separately to the channels. The pulse width is common to all channels, and is determined by setup data. The allowable range is 0 - 104.45msec.

This command issues the value +19h" to the output port +16, and sets a pulse width on the output port +17.

The width of a one-shot pulse can be determined according to the following expression:

Table 4.9. Relationship between One-Shot Pulse Setup Data and the Pulse Width

pulse width-setting data x 409.6 = pulse width [msec]

| Г |    | C            | ne_sh | ot_pul | se wid | th set | ting da       | nta |     |                    |

|---|----|--------------|-------|--------|--------|--------|---------------|-----|-----|--------------------|

|   | D7 | $\leftarrow$ |       |        |        |        | $\rightarrow$ | D0  | [h] | Pulse width        |

|   | 0  | 0            | 0     | 0      | 0      | 0      | 0             | 0   | 00h | 0                  |

|   | 0  | 0            | 0     | 0      | 0      | 0      | 0             | 1   | 01h | Approx. 409.6µsec  |

|   | 0  | 0            | 0     | 0      | 0      | 0      | 1             | 0   | 02h | Approx. 819.2μsec  |

|   | 0  | 0            | 0     | 0      | 0      | 0      | 1             | 1   | 03h | Approx. 1.23msec   |

|   | 0  | 0            | 0     | 0      | 1      | 1      | 0             | 0   | 0Ch | Approx. 4.92msec   |

|   | 0  | 0            | 0     | 1      | 1      | 0      | 0             | 1   | 19h | Approx. 10.24msec  |

|   | 0  | 0            | 1     | 1      | 0      | 0      | 0             | 1   | 31h | Approx. 20.07msec  |

|   | 0  | 1            | 0     | 0      | 1      | 0      | 0             | 1   | 49h | Approx. 29.9msec   |

|   | 0  | 1            | 1     | 0      | 0      | 0      | 1             | 0   | 62h | Approx. 40.14msec  |

| Е | 0  | 1            | 1     | 1      | 1      | 0      | 1             | 0   | 7Ah | Approx. 49.97msec  |

|   | 1  | 0            | 0     | 1      | 0      | 0      | 1             | 1   | 93h | Approx. 60.2msec   |

|   | 1  | 0            | 1     | 0      | 1      | 0      | 1             | 1   | ABh | Approx. 70.04msec  |

|   | 1  | 1            | 0     | 0      | 0      | 1      | 0             | 0   | C4h | Approx. 80.28msec  |

|   | 1  | 1            | 0     | 1      | 1      | 1      | 0             | 0   | DCh | Approx. 90.11msec  |

|   | 1  | 1            | 1     | 1      | 0      | 1      | 0             | 1   | F5h | Approx. 100.35msec |

|   | 1  | 1            | 1     | 1      | 1      | 1      | 1             | 1   | FFh | Approx. 104.45msec |

<sup>\*</sup>represents the initial state

#### Notes!

- The initial condition is pulse width = 0 (no output) (00h).

- The pulse width is subject to some variable depending upon connection load specifications.

## Initialization

When the power is turned on or the system is reset, the following initial settings are effected:

Table 4.10. Initial Settings

| Item                   | Initial settings                               |

|------------------------|------------------------------------------------|

| Operation mode         | 00h                                            |

| Z-phase CLR input      | 04h (enabled only for Z-phase one-time input)  |

| COMPARE register       | 0                                              |

| READ register          | Not available                                  |

| 24-bit UP/DOWN counter | 000000h                                        |

| Digital filter         | 00h (0.1msec)                                  |

| Status data            | 7Bh (when not connected to an external device) |

| Count-value latch      | 00h                                            |

| Interrupt mask         | 1Fh (all interrupts disabled)                  |

| Sense port             | 00h                                            |

| Timer data             | 00000000h                                      |

| Timer start            | 00h (timer stopped)                            |

| One-shot pulse         | 00h (no output)                                |

# **Examples**

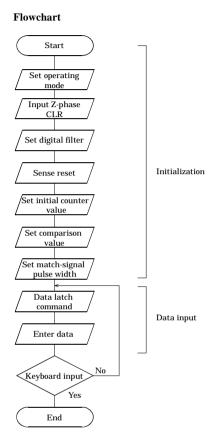

## 2-Phase Pulse Count (no interrupts)

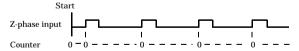

Figure 4.18. 2-Phase Pulse Count (No Interrupts)

```

Sample Program

Sample program 1

0

2-Phase, Asynchronous Clear, Normal Count

000000H

000064H

DEVICE ID:

Mode:

Initial Data:

Compare Data:

Compare Data: 00000411 Channel: 0ch Programmable Timer: N/A Digital Filter 6.5 used Interrupt: N/A

-----<del>-</del>-----*/

#include <stdio.h>

#include <conio.h>

/* ---- Constant -----

#define ADR

#define CH

/* ---- Declarations -----

/* 8-bit */

/* lower */

/* middle */

/* upper */

/* reserved */

struct REGS08 {

unsigned char lower;

unsigned char middle;

unsigned char upper;

unsigned char reserved;

truct REGS24 { unsigned long count;

struct

/* 24-bit */

union ACCESS {

struct

REGS08

Byte[CH];

Whole[CH];

/* 8-bit */

/* 24-bit */

struct

REGS24

REGS08

struct

Byte[CH];

Whole[CH];

struct REGS24

union ACCESS CountData

union ACCESS CompData;

/* 24-bit */

CountData;

/* ---- Prototype ----- */

void main(void);

void Initialize( unsigned char); /* initialize */

void ReadData( unsigned char, unsigned long *, unsigned char *);

/* read data */

/* ---- Initialize ----- */

yoid Initialize (unsigned char ch)

outp( ADR+0x10, ch*5+1); /* mode set */

outp( ADR+0x11, 0x8c);

outp( ADR+0x11, 0x8c);

outp( ADR+0x11, 0x4c);

outp( ADR+0x11, 0x4c);

outp( ADR+0x11, 0x4c);

outp( ADR+0x11, 0x4c);

outp( ADR+0x10, ch*5+4); /* digital filter set */

outp( ADR+0x10, 0x16c); /* sense reset */

outp( ADR+0x10, 0x16c); /* sense reset */

outp( ADR+0x11, 0xff;

outp( ADR+0x11, 0xff;

outp( ADR+0x11, CountData.Byte[ch].lower); /* lower */

outp( ADR+0x11, CountData.Byte[ch].middle); /* middle */

outp( ADR+0x11, CountData.Byte[ch].upper); /* upper */

outp( ADR+0x11, CountData.Byte[ch].upper); /* upper */

outp( ADR+0x11, CompData.Byte[ch].lower); /* lower */

outp( ADR+0x11, CompData.Byte[ch].lower); /* lower */

outp( ADR+0x11, CompData.Byte[ch].middle); /* middle */

outp( ADR+0x11, CompData.Byte[ch].upper); /* upper */

outp( ADR+0x11, CompData.Byte[ch].upper); /* lower */

outp( ADR+0x11, CompData.Byte[ch].upper); /* upper */

```

## 2-Phase Pulse Count (with interrupts)

### **Flowchart** Start (Interrupt processing) Data latch Initialize command Enter data Set timer Change interrupt No Final channel? Yes Set an interrupt level Count the number of interrupts Start timer Sense reset Show data EOI End of interrupt? Return Stop timer Reset the interrupt level Restore interrupt vector End

Figure 4.19. 2-Phase Pulse Count (with Interrupts)

```

Sample Program

Sample program 2

DEVICE ID:

0 2-Phase, Asynchronous Clear, Normal Count {\tt 000000H}

Mode:

Initial Data:

Compare Data:

000064H

0 to 1ch

1 sec

6.5 used

IRQ5 10 times

Channel:

Programmable Timer:

Digital Filter

Interrupt:

*/

#include <stdio.h>

#include <conio.h>

#include <dos.h>

/* ---- Constant ----- */

#define ADR

#define CH

#define IRQ5

#define IRQ7

#define IRQ9

/* I/O address */

/* channel */

/* IRO5 */

/* IRQ9 */

0x0800

2

/* ---- Declarations ----- */

/* 8-bit */

/* lower */

/* middle */

struct REGS08

unsigned char lower;

unsigned char middle;

unsigned char upper;

unsigned char reserved;

/* upper */

/* reserved */

};

struct REGS24 {

unsigned long count;

/* 24-bit */

};

union ACCESS {

Byte[CH];

Whole[CH];

/* 8-bit */

/* 24-bit */

REGS08

struct

struct

REGS24

};

ACCESS

ACCESS

REGS08

volatile union volatile union

CountData:

CompData;

Byte[CH];

Whole[CH];

/* 8-bit */

/* 24-bit */

struct

REGS24

struct

volatile int volatile int int

intcnt = 0;    /* interrupt counter */

IrqLevel = IRQ5;    /* interrupt level */

OrgMasterImr, OrgSlaveImr;    /* original IMR */

unsigned char IntVector[3] = { 0x0d, 0x0f, 0x71 };

unsigned char PicMask[3] = { 0xdf, 0x7f, 0xfd };

unsigned char IsrClear[3] = { 0x6f, 0x7f, 0xfd };

unsigned char IsrClear[3] = { 0x65, 0x67, 0x61 };

unsigned char IntEnable[3] = { 0x81, 0x82, 0x84 };

/* interrupt enable */

/* ---- Prototype ----- */

/* ---- Flootype

void main(void);

void Initialize(unsigned char); /* initialize */

void Interval(void); /* timer set */

void ChgVect(void); /* change vector */

void Display(void); /* display */

void ResVect(void); /* restore vector */

void _interrupt _far inthandler(void); interrupt handler */

void ( _interrupt _far *OrgVect)();

/* original interrupt vector */

/* ---- Initialize ----- */

```

Initialize (unsigned char ch)

```

outp( ADR+0x10, ch*5+1 );

/* mode set */

outp

ADR+0x11,

0x8c);

ch*5+2);

ADR+0x10,

outp

/* z-pulse set */

0x4 );

0x4 );

ch*5+4 );

0x1 );

0x16 );

0xff (;

ADR+0x11,

outp

ADR+0x10,

outp

/* digital filter set */

ADR+0x11,

outp

ADR+0x10,

outp

/* sense reset */

ADR+0x11,

outp

Oxff );

ch*5 );

CountData.Byte[ch].lower ); /* lower */

CountData.Byte[ch].middle ); /* middle */

CountData.Byte[ch].upper ); /* upper */

ContData.Byte[ch].lower ); /* upper */

CompData.Byte[ch].lower ); /* lower */

CompData.Byte[ch].middle ); /* middle */

CompData.Byte[ch].upper ); /* upper */

Ox19 ); /* one-shot pulse set */

Oxff );

ADR+0x10,

outp

ADR+0x11,

ADR+0x11,

ADR+0x11,

outp

outp

outp

ADR+0x10,

outp

ADR+0x11,

ADR+0x11,

ADR+0x11,

ADR+0x11,

outp

outp

ADR+0x10, 0x19);

ADR+0x11, 0xff);

outp(

/* ---- timer set ----- */

void Interval( void )

outp(outp(outp(

0x15 );

0xf );

0x17 (;

0xff );

0x2c );

0x31 );

ADR + 0 \times 10,

/* mask clear */

ADR+0x11;

ADR+0x10,

/* timer set */

/* 1 sec */

ADR+0x11,

ADR+0x11,

ADR+0x11,

outp(

outp (

outp( ADR+0x11, 0x31 ) outp( ADR+0x11, 0x1 );

/* ---- change vector ----- */

void ChqVect( void )

OrgVect = _dos_getvect( IntVector[IrqLevel] );

disable();

} else

_enable();

/* enable */

/* ---- display ----- */

yoid Display( void )

printf("interrupt count = %03d \n", intcnt);

/* ----- restore vector ----- */

void ResVect( void )

/* disable */

/* restore IMR */

disable();

utsapie();

if ( IrqLevel > IRO7 ) {

outp( 0x21, OrgMasterImr );

outp( 0xa1, OrgSlaveImr );

} else

} else '

outp( 0x21, OrgMasterImr );

_dos_setvect( IntVector[IrqLevel], OrgVect );

_/* restore orgvect */

/* enable */

_enable();

/* ---- interrupt handler ----- */

void interrupt far inthandler( void )

```

```

unsigned char i;

_enable():

/* enable */

CountData.Byte[i].middle = (unsigned char)inp( ADR+0x11 ); /* middle */

CountData.Byte[i].upper = (unsigned char)inp( ADR+0x11 ); /* upper */

CountData.Whole[i].count &= 0xffffff;

intcnt++;

outp( ADR+0x10, 0x16 );

outp( ADR+0x11, 0x10 );

_disable();

/* count interrupt */

/* sense reset */

/* disable */

if ( IrqLevel > IRQ7 ) {

outp( 0xa0, 0x20 );

outp( 0xa0, 0x0b );

if (!inp( 0xa0 ) ) outp( 0x20, 0x20 );

} else   outp( 0x20, 0x20 );

/* EOI */

/* ----- main ----- */

yoid main( void )

unsigned char i;

for (i = 0; i < CH; i++) {

CountData.Whole[i].count = 0x000000; /* count data */

CompData.Whole[i].count = 0x000064;/* compare data */

Initialize(i); /* initialize */</pre>

Interval();

ChgVect();

outp( ADR+0x2, IntEnable[IrqLevel] );/* change vector */

outp( ADR+0x10, 0x18 ); /* interrupt level */

outp( ADR+0x11, 0x1 );

while( intcnt < 10 )

Display();</pre>

/* display */

Display();

outp( ADR+0x10, 0x18 );

outp( ADR+0x11, 0x0 );

outp( ADR+0x2, 0x0 );

ResVect();

/* display */

/* timer stop */

/* interrupt level */

/* restore vector */

}

/* ----- End of file --- */

```

# 5. Using the Memory Address Map

When connected to a CPU-CAxx(FIT)GY, the CNT24-2(FIT)GY can be accessed by a host computer through a network. In addition, the Module can be allocated to the memory controlled by the Controller Module according to a given Device ID. Applications running on the host computer control the I/O modules by reading/writing the memory that is controlled by the Controller Module.

For detailed specifications on the memory controlled by the Controller Module, see the Controller Module manual

Following is an explanation of the memory areas necessary for the use of the CNT24-2(FIT)GY: the "module settings area", the "module information area", and the "basic output data area.

#### **Module Settings Area**

This area controls the settings and how the module is started.

The module becomes available when the necessary settings are written into this area and the module activation option is set in the [module startup register].

#### **Module Information Area**

The current module settings are stored in this area.

When the Module is started, the contents of the Module Settings Area are copied to the Module Information Area. By reading this area, you can verify the current module settings.

#### Basic Input Data Area

Basic input data is read in this area.

#### Basic Output Data Area

Basic output data is written in this area.

## **Module Settings Area**

The module settings area is a 128-byte (80h) area beginning at address 301000h, and corresponds to a given Device ID.

The starting address can be determined according to the following expression:

Starting address =  $301000h + 80h \times (Device ID)$

Table 5.1. Module Settings Area < 1/2 >

| Address(h)                                   | Area                | Item                                          | Size | Access<br>type | Initial<br>value(h) | Initial<br>settings                  |

|----------------------------------------------|---------------------|-----------------------------------------------|------|----------------|---------------------|--------------------------------------|

| Starting address+00                          |                     | Module type (category)                        | 1    | R              | 03                  |                                      |

| Starting address+01                          |                     | Module type                                   | 1    | R              | 00                  | CNT24-2(FIT)GY                       |

|                                              |                     | (serial No.)                                  |      |                |                     |                                      |

| Starting address+02                          |                     | System-reserved<br>(revision No.)             | 1    | R              | None                |                                      |

| Starting address+03                          |                     | Supported functions                           | 1    | R              | 03                  | Basic input                          |

| Starting address+04                          |                     | Number of<br>basic input channels             | 1    | R              | 02                  | 2channels                            |

| Starting address+05                          |                     | Basic input data size                         | 1    | R              | 08                  | 8bytes                               |

| Starting address+06                          | Module-<br>specific | Number of basic output channels               | 1    | R              | 02                  | 2channels                            |

| Starting address+07                          | information         | Basic output data size                        | 1    | R              | 08                  | 8bytes                               |